2018年1月25日

各位

# ファンアウト・パネルレベルパッケージ用ガラスキャリア付き

# 微細回路形成用材料「HRDP®」を開発 ~ジオマテック株式会社と共に、量産化を目指す~

当社(代表取締役社長 西田計治)は、ファンアウト・パネルレベルパッケージ用ガラスキャリア付き微細回路形成用材料「 $HRDP^{@*1}$ 」を開発し、ジオマテック株式会社(代表取締役社長 松﨑建太郎)と $HRDP^{@}$ の量産技術を確立しましたので、お知らせいたします。

IoT 時代の高い要求性能に対応するスマートフォン等のパッケージ基板には、MSAP 工法 $^{*2}$ による微細配線を形成する材料として、当社極薄銅箔「MicroThin $^{TM}$ \*3」が広く採用されています。更に今般では、極薄銅箔を用いた SAP 工法 $^{*4}$ による微細配線化も実用化されていますが、これら工法の限界領域を超えるものとして Chip 1<sup>st</sup> 工法 $^{*5}$  による FO-WLP $^{*6}$ (ファンアウト・ウエハーレベルパッケージ)が注目されています。しかしながら、この工法は歩留まり、製造コストの課題があります。

そこで期待されているのが RDL 1<sup>st</sup> 工法<sup>\*7</sup>でのファンアウト・パネルレベルパッケージ<sup>\*8</sup>です。 この工法では、RDL 形成後に半導体チップ実装を行うことで良品チップのロスリスクを回避し、パネルレベルでの生産ができるため、高歩留りで、かつ低コスト化が可能となります。この度、当社ではファンアウト・パネルレベルパッケージの普及に貢献する材料として「HRDP<sup>®</sup>」を開発いたしました。

尚、本製品を用いれば、 $L/S=2/2 \mu \, m^{**9} \, \nu$ ベルの微細配線を形成できることを確認しており、既に複数の電子デバイスメーカーとサプライチェーン各社において評価が進捗しています。

当社のスローガンである「マテリアルの知恵を活かす」のもと、お客様の声を形にして、安定した品質を維持するため、優れた薄膜成膜技術を持つジオマテック株式会社と共創・協働し、お客様への十分な供給能力を確保してまいります。

以上

### 【お問い合わせ先】

三井金属鉱業株式会社経営企画本部広報部TEL 03-5437-8028FAX 03-5437-8029EメールアドレスPR@mitsui-kinzoku.co.jp

#### 【用語解説他】

- ※1 High Resolution De-bondable Panel (詳細は別紙「技術の紹介」をご参照願います。)

- ※2 Modified Semi Additive Process

- ※3 MicroThin<sup>TM</sup>: 当社キャリア付極薄銅箔

- ¾4 Semi Additive Process

- ※5 Chip 1st (最初に半導体チップをキャリアに配置する工法)

- ※7 Re-Distribution Layer 1<sup>st</sup> (最初に再配線層を形成する工法) (詳細は別紙「技術の紹介」をご参照願います。)

- ※8 Fan Out Panel Level Package (詳細は別紙「技術の紹介」をご参照願います。)

- ※9 L/S= $2/2 \mu$  m : 配線の幅(Line :  $2 \mu$  m)と隣り合う配線同士の間隔(Space :  $2 \mu$  m)

#### ご参考(2017年9月末現在)

### 【ジオマテック株式会社の概要】

所在地:横浜市西区みなとみらい二丁目2番1号横浜ランドマークタワー9F

代表取締役社長:松﨑 建太郎

資本金: 40 億 4,385 万円

従業員数:595名(連結)、443名(単体)

事業内容:フラットパネルディスプレイ用基板(液晶ディスプレイ用基板、OLED 用基板、タッチパネル用基板)、光学機器用部品、固体レーザー用光学系部品、その他真空成膜製品の製造及び販売他

#### 【技術の紹介】

#### 1. 開発商品 HRDP®

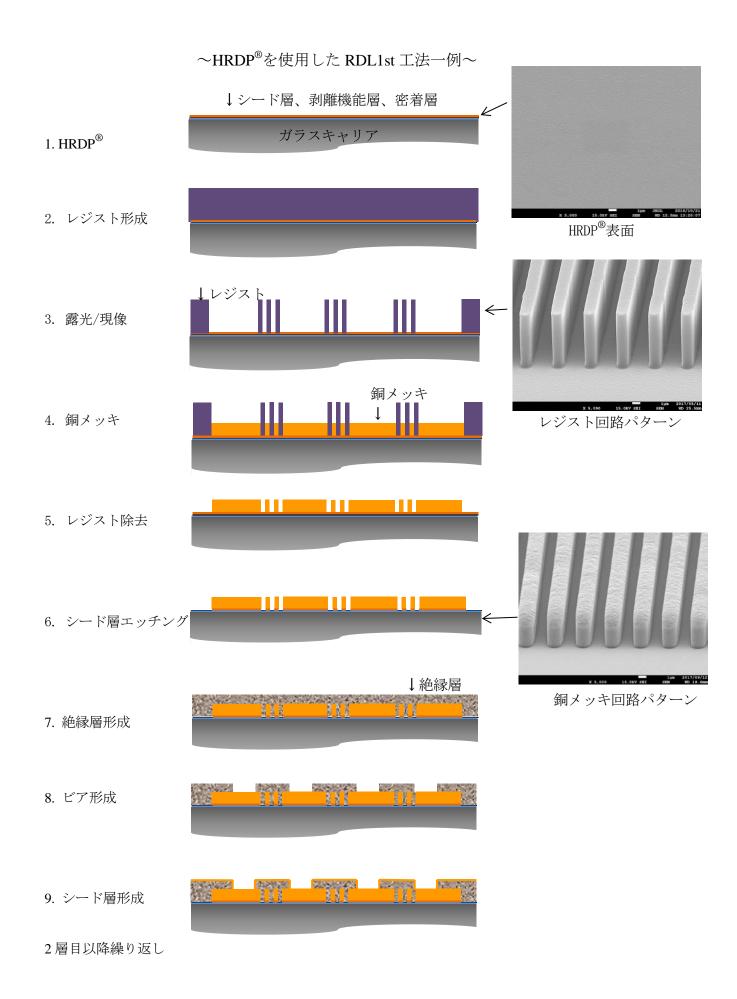

HRDP<sup>®</sup>は、ガラスキャリア表面上に多層薄膜を形成した構造となっています(写真1、図1)。 その特徴は、高い平坦性を有するガラスキャリア上に形成された極薄の「メッキ用シード層」 によって超微細な RDL をパネルサイズ (例 600×600mm) で形成でき、また「剥離機能層」に よって 260℃の熱負荷後でも安定な機械的ガラスキャリアの取り外しが可能になります。

写真 1 HRDP®表面外観写真

図1 HRDP®の断面構造模式図

## 2. HRDP®を使用したファンアウト・パネルレベルパッケージの製造工程

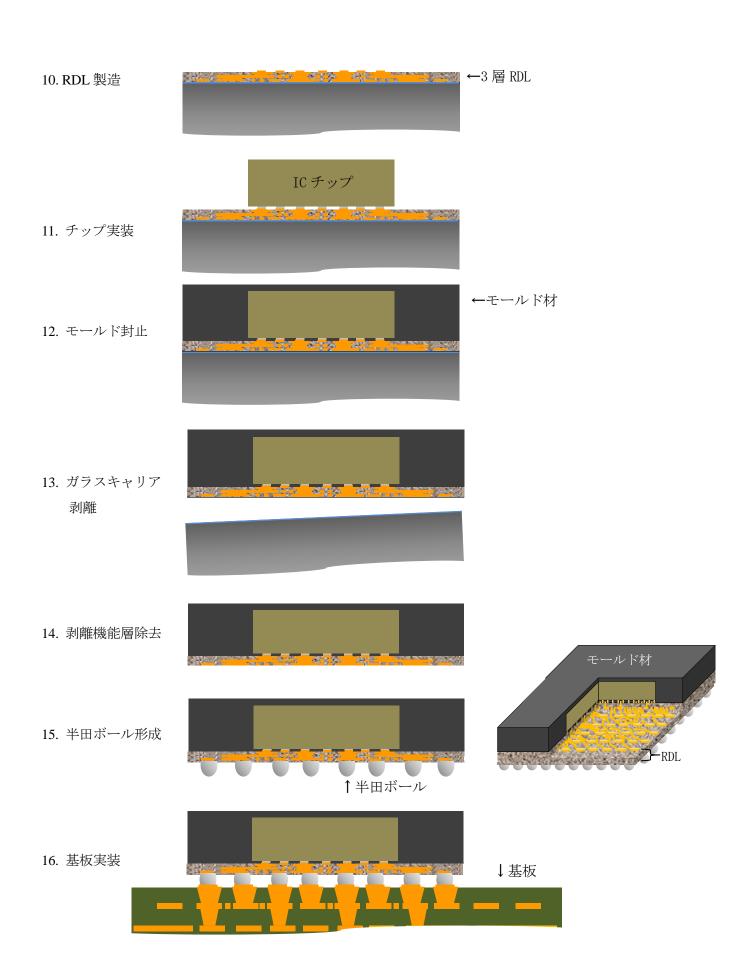

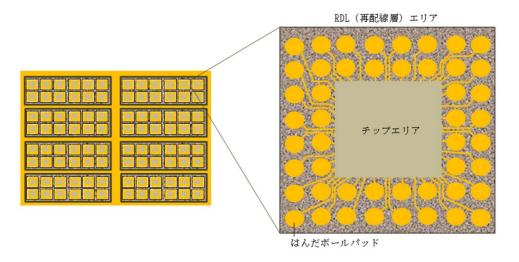

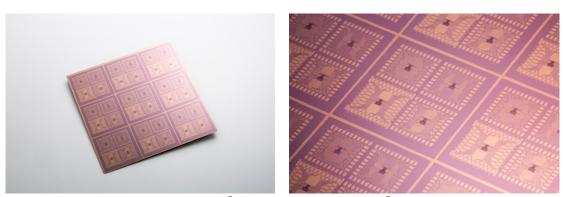

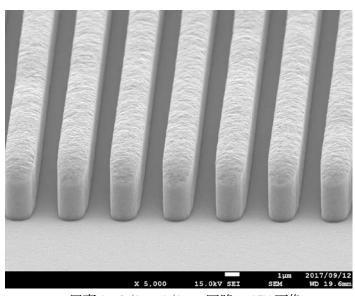

HRDP®を使用した RDL 1<sup>st</sup> 工法の一例(図 2)とファンアウト・パネルレベルパッケージの構造(図 3、写真 2)を以下に示します。HRDP®上にレジスト形成、露光/現像、銅メッキ、レジスト除去、メッキ用シード層エッチング、絶縁層形成、ビア形成、シード層形成を繰り返し、RDL を製造します。その後、シリコンチップをフリップチップ実装した後にモールド材で封止し、剥離機能層と密着層間にてガラスキャリアを剥離し、回路側に残存した剥離層をエッチングで取り除きます。HRDP®を使用した回路形成では、L/S =  $2/2 \, \mu$  m が可能であることを確認しています(写真 3)。

図 2 HRDP<sup>®</sup>を使用した RDL 1<sup>st</sup> 工法の一例

図3 ファンアウト・パネルレベルパッケージの構造模式図 (左:パネルサイズ RDL、右:パッケージ部拡大)

写真 2 回路形成後の HRDP<sup>®</sup>表面外観写真(左: HRDP<sup>®</sup>全景、右: 拡大図)

写真3  $L/S = 2/2 \mu m$ 回路の SEM 画像